MEMS is the technology of microscopic devices incorporating both electronic and moving parts. MEMS are made up of components between 1 and 100 micrometers in size, and MEMS devices generally range in size from 20 micrometres to a millimetre, although components arranged in arrays can be more than 1000 mm2. They usually consist of a central unit that processes data and several components that interact with the surroundings.

Nitric acid is the inorganic compound with the formula HNO3. It is a highly corrosive mineral acid. The compound is colorless, but older samples tend to be yellow cast due to decomposition into oxides of nitrogen. Most commercially available nitric acid has a concentration of 68% in water. When the solution contains more than 86% HNO3, it is referred to as fuming nitric acid. Depending on the amount of nitrogen dioxide present, fuming nitric acid is further characterized as red fuming nitric acid at concentrations above 86%, or white fuming nitric acid at concentrations above 95%.

Semiconductor device fabrication is the process used to manufacture semiconductor devices, typically integrated circuits (ICs) such as computer processors, microcontrollers, and memory chips that are present in everyday electrical and electronic devices. It is a multiple-step photolithographic and physico-chemical process during which electronic circuits are gradually created on a wafer, typically made of pure single-crystal semiconducting material. Silicon is almost always used, but various compound semiconductors are used for specialized applications.

Red fuming nitric acid (RFNA) is a storable oxidizer used as a rocket propellant. It consists of 84% nitric acid, 13% dinitrogen tetroxide and 1–2% water. The color of red fuming nitric acid is due to the dinitrogen tetroxide, which breaks down partially to form nitrogen dioxide. The nitrogen dioxide dissolves until the liquid is saturated, and produces toxic fumes with a suffocating odor. RFNA increases the flammability of combustible materials and is highly exothermic when reacting with water.

Hydrofluoric acid is a solution of hydrogen fluoride (HF) in water. Solutions of HF are colourless, acidic and highly corrosive. It is used to make most fluorine-containing compounds; examples include the commonly used pharmaceutical antidepressant medication fluoxetine (Prozac) and the material PTFE (Teflon). Elemental fluorine is produced from it. It is commonly used to etch glass and silicon wafers.

The planar process is a manufacturing process used in the semiconductor industry to build individual components of a transistor, and in turn, connect those transistors together. It is the primary process by which silicon integrated circuit chips are built. The process utilizes the surface passivation and thermal oxidation methods.

Chemical mechanical polishing (CMP) or planarization is a process of smoothing surfaces with the combination of chemical and mechanical forces. It can be thought of as a hybrid of chemical etching and free abrasive polishing.

Porous silicon is a form of the chemical element silicon that has introduced nanopores in its microstructure, rendering a large surface to volume ratio in the order of 500 m2/cm3.

The etch pit density (EPD) is a measure for the quality of semiconductor wafers.

![<span class="mw-page-title-main">Piranha solution</span> [Per-hexa-sulfuric acid] is an oxidizing acid mixture containing sulfuric acid and hydrogen peroxide](https://upload.wikimedia.org/wikipedia/commons/thumb/3/30/The_Piranha_Solution.png/320px-The_Piranha_Solution.png)

Piranha solution, also known as piranha etch, is a mixture of sulfuric acid (H2SO4) and hydrogen peroxide (H2O2). The result of the mixture gives rise to a strong union of two acids called per-hexa-sulfuric acid (H4SO6) that is used to clean organic residues off substrates. Because the mixture is a strong oxidizing agent, it will decompose most organic matter, and it will also hydroxylate most surfaces (by adding –OH groups), making them highly hydrophilic (water-compatible). This means the solution can also easily dissolve fabric and skin, potentially causing severe damage and chemical burns in case of inadvertent contact.

The RCA clean is a standard set of wafer cleaning steps which need to be performed before high-temperature processing steps of silicon wafers in semiconductor manufacturing.

In microfabrication, thermal oxidation is a way to produce a thin layer of oxide on the surface of a wafer. The technique forces an oxidizing agent to diffuse into the wafer at high temperature and react with it. The rate of oxide growth is often predicted by the Deal–Grove model. Thermal oxidation may be applied to different materials, but most commonly involves the oxidation of silicon substrates to produce silicon dioxide.

Etching is used in microfabrication to chemically remove layers from the surface of a wafer during manufacturing. Etching is a critically important process module, and every wafer undergoes many etching steps before it is complete.

Buffered oxide etch (BOE), also known as buffered HF or BHF, is a wet etchant used in microfabrication. Its primary use is in etching thin films of silicon dioxide (SiO2) or silicon nitride (Si3N4). It is a mixture of a buffering agent, such as ammonium fluoride (NH4F), and hydrofluoric acid (HF). Concentrated HF (typically 49% HF in water) etches silicon dioxide too quickly for good process control and also peels photoresist used in lithographic patterning. Buffered oxide etch is commonly used for more controllable etching.

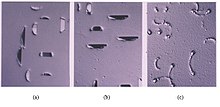

Direct bonding, or fusion bonding, describes a wafer bonding process without any additional intermediate layers. The bonding process is based on chemical bonds between two surfaces of any material possible meeting numerous requirements. These requirements are specified for the wafer surface as sufficiently clean, flat and smooth. Otherwise unbonded areas so called voids, i.e. interface bubbles, can occur.

Anodic bonding is a wafer bonding process to seal glass to either silicon or metal without introducing an intermediate layer; it is commonly used to seal glass to silicon wafers in electronics and microfluidics. This bonding technique, also known as field assisted bonding or electrostatic sealing, is mostly used for connecting silicon/glass and metal/glass through electric fields. The requirements for anodic bonding are clean and even wafer surfaces and atomic contact between the bonding substrates through a sufficiently powerful electrostatic field. Also necessary is the use of borosilicate glass containing a high concentration of alkali ions. The coefficient of thermal expansion (CTE) of the processed glass needs to be similar to those of the bonding partner.

Plasma-activated bonding is a derivative, directed to lower processing temperatures for direct bonding with hydrophilic surfaces. The main requirements for lowering temperatures of direct bonding are the use of materials melting at low temperatures and with different coefficients of thermal expansion (CTE).

Eutectic bonding, also referred to as eutectic soldering, describes a wafer bonding technique with an intermediate metal layer that can produce a eutectic system. Those eutectic metals are alloys that transform directly from solid to liquid state, or vice versa from liquid to solid state, at a specific composition and temperature without passing a two-phase equilibrium, i.e. liquid and solid state. The fact that the eutectic temperature can be much lower than the melting temperature of the two or more pure elements can be important in eutectic bonding.

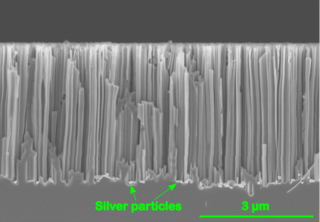

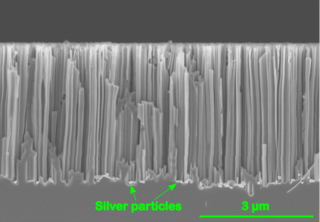

Metal Assisted Chemical Etching is the process of wet chemical etching of semiconductors with the use of a metal catalyst, usually deposited on the surface of a semiconductor in the form of a thin film or nanoparticles. The semiconductor, covered with the metal is then immersed in an etching solution containing and oxidizing agent and hydrofluoric acid. The metal on the surface catalyzes the reduction of the oxidizing agent and therefore in turn also the dissolution of silicon. In the majority of the conducted research this phenomenon of increased dissolution rate is also spatially confined, such that it is increased in close proximity to a metal particle at the surface. Eventually this leads to the formation of straight pores that are etched into the semiconductor. This means that a pre-defined pattern of the metal on the surface can be directly transferred to a semiconductor substrate.

Vapor etching refers to a process used in the fabrication of Microelectromechanical systems (MEMS) and Nanoelectromechanical systems (NEMS). Sacrificial layers are isotropically etched using gaseous acids such as Hydrogen fluoride and Xenon difluoride to release the free standing components of the device.

![<span class="mw-page-title-main">Piranha solution</span> [Per-hexa-sulfuric acid] is an oxidizing acid mixture containing sulfuric acid and hydrogen peroxide](https://upload.wikimedia.org/wikipedia/commons/thumb/3/30/The_Piranha_Solution.png/320px-The_Piranha_Solution.png)